Overview

RISER will develop the first all-European RISC-V cloud server infrastructure, significantly enhancing Europe’s open strategic autonomy. RISER will leverage and validate open hardware high-speed interfaces combined with a fully-featured operating system environment and runtime system, enabling the integration of low-power components, including RISC-V processor chips from the EPI and EUPILOT projects, in a novel energy-efficient cloud architecture.

Scope

RISER aims to develop and validate open-source designs for standardized form-factor system platforms suitable for supporting cloud services and deploying cloud applications. RISER plans to play a leading role in enabling the path towards a European-based cloud infrastructure and towards the first RISC-V cloud architecture using the technology being developed within the EPI and EUPilot projects. We aim for RISER to be the technological enabler for larger EU initiatives.

Project Information

RISC-V for cloud services

Call: HORIZON-CL4-2022-DIGITAL-EMERGING-01-26 / Open source for cloud-based services

Grant Agreement: 101092993, European Health and Digital Executive Agency (HaDEA)

Budget: € 5.316.125,00

Duration: 01 Jan 2023 – 31 Dec 2025 (36 months)

https://cordis.europa.eu/project/id/101092993

Ambition

RISC-V is an open source ISA defined by the RISC-V Foundation, which rapidly managed to attract hundreds of international institutions, including universities, research institutions and companies worldwide, that consistently contribute to its design, implementation, and worldwide adoption. The RISER project will provide the first opportunity to have a European RISC-V cloud infrastructure, powering a real pre-production cloud architecture, developed by core members of the EPI and EUPilot projects. The project will deliver a large number of novel features at different levels. Next, we describe the current state of the art on the topics and the main advances we are aiming to achieve.

Embracing hyperconvergence, the RISER architecture allows for distributed storage and memory to be used by any processor in the system with low overhead. The internal NoC of the EPI and EUPilot chips are directly connected via Chip-to-Chip links and on-board QSFP connectors in order to allow for a direct communication between the processor and system resources. In this way, traffic can be directly routed between the processors, so that any processor can directly access remote memories, storage and network resources. Partitioned global address space (PGAS) involving a global memory address space abstraction logically partitioned can be easily deployed to increase throughput and minimize latency.

Beyond the SOTA: The PGAS memory model is usually abstracted by the operating system implemented by SW libraries and/or hardware support which may result in energy increase and performance degradation. RISER supports a PGAS system and hyperconverged resources by design (i.e. with hardware support) where any processor in the system can directly access local or remote memory, storage and network resources through the directly interconnected processor chips. The Chip-to-Chip links transport the AMBA5 CHI protocol and enable I/O coherence which in-turn allows maintaining data coherency and consistency between the processors and I/O devices of a PGAS system directly in hardware.

In RISER, the Chip-to-Chip (C2C) interconnect provided by EXTOLL will be used to connect the different processor chips. The interconnect is implemented within EPI and EUPilot chips to match the bandwidth required by the vector units: multiple C2C lanes providing 64GB/s and in addition LPDDR4 interfaces provide 33GB/s to local DRAM.

Beyond the SOTA: In RISER, the I/O capabilities of the EPI and EUPilot chips will be augmented with 100 GigE and NVMe storage devices. We will connect, expand and optimize the I/O interfaces, include device drivers and low-level firmware (FPGA design and primitives) so that we can derive an efficient microserver architecture with high performance storage and communication to offer the required performance and power characteristics for cloud application and services.

A crucial challenge in today’s cloud systems is how to increase energy efficiency. This challenge can be addressed in several layers of the system architecture. At the lower hardware layers energy efficient components, such as low-power processors, memories and storage devices can be used. At a higher layer energy-efficient communication protocols and topologies can be employed in order to decrease the number of messages exchanged between processors, memories and I/O devices as well as the distance between them. Finally, at the software level, energy-efficient device drivers and applications can be developed to further decrease the processing and memory operations. RISER adheres to this energy efficient approach so that system resources can be used efficiently by cloud applications.

Beyond the SOTA: RISER employs a large number of interconnected low-power components that are usually found in IoT devices without sacrificing performance, since the RISER architecture matches the needs of today’s cloud applications, which expose a lot of parallelism and run in parallel requiring a large number of scale-out.

Over the last few years, there has been a tremendous technology improvement in cloud computing to address the demanding needs of today’s applications and users. Although such technologies have managed to improve productivity dramatically, they are extremely demanding in terms of resources, including CPU, memory, network throughput, and even I/O. They have been shown to be able to leverage the huge computing power of different classes of CPUs and accelerators14, but not in the RISC-V domain yet.

Beyond the SOTA: In the project, we will provide two advanced infrastructures, based on European technologies, that will enable a broad class of cloud technologies to be efficiently deployed on the RISER RISCV architecture. Thus RISER will contribute to making RISC-V a competitive alternative in this field. We will develop the necessary firmware and the I/O device drivers, and port a cloud software framework so that the platform can be used efficiently by cloud providers and users.

The RISER project is developing a European cloud infrastructure, which initiated the indispensable activities for an all-European ecosystem.

Beyond the SOTA: The RISER system will be European all the way from the top of the software stack down to the hardware platform and processors. This infrastructure, furthermore, features open hardware and software which reflects the European culture of collaboration of many stakeholders where the end product is more than the sum of its parts thanks to easily shareable IP developed in the project. Every aspect of the project, from the device drivers and the boot firmware to the Printed Circuit Board (PCB) design, FPGA design, the hardware interfaces and the processors will be completely developed and owned by Europe. Perhaps the only technology in the project that will be sourced external to Europe will be the CAD tools, however the impact is minimal since these products will just be used as external tools – rather than be developed or modified. The board form factors and interfaces will follow open standards to be easily used in other environments. The RISER platforms will be open so that users outside of the project including partners from contemporary projects in the call can access them easily.

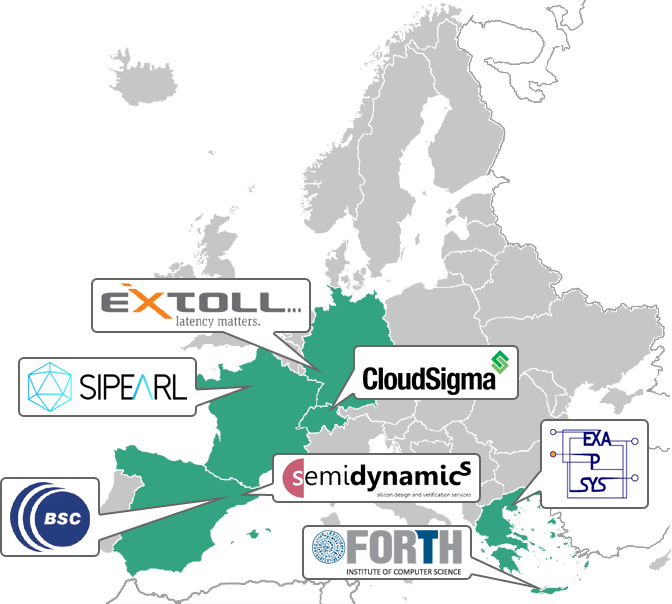

Partners

RISER partners’ roles

Foundation for Research and Technology – Hellas (FORTH):

Project coordinator, leads Firmware and System Software development, with contributions to boot and OS support for RISER platforms. Contributes to platform development, leading the microserver I/O firmware task. Leads the networked object store use-case.

Exascale Performance Systems (EXAPSYS):

Leads Hardware Platform Prototyping, with contributions to the PCIe accelerator and microserver platform designs. Responsible for the manufacturing of RISER PCBs and component assembly.

Semidynamics Technology Services S.L. (SemiDynamics):

Leads Architecture and Verification, with contributions to the verification framework for the RISER platforms. Leads the FPGA-based emulator platform task.

Barcelona Supercomputing Center (BSC):

Leads Use Cases and Evaluation, with contributions to the accelerator use case. Leads the task on standards and the Open Access Programme.

SIPEARL SAS (SIPEARL):

Leads the requirements capture task and the dissemination and communication. Contributes to the development and verification of the PCI acceleration platform, particularly regarding the host server interface. Responsible for providing dedicated Rhea servers for the acceleration use case.

CloudSigma AG (CloudSigma):

Leads Dissemination, Exploitation and Standardization, with contributions to planning dissemination and communication actions, and tracking exploitation and use over the project timeline. Leads the final evaluation task.

EXTOLL GMBH (EXTOLL):

Leads the architecture and specifications task. Contributes to RISER platform development, particularly to the use of high-speed links for interfacing among PCB components and with I/O peripherals.

Contact us

Postal Address

Foundation for Research and Technology – Hellas (FORTH)

Institute of Computer Science (ICS)

N. Plastira 100

Vassilika Vouton, GR-70013

Heraklion, Crete, GREECE

Contact Persons:

Dr. Manolis Marazakis | maraz@ics.forth.gr | +30 2810391699

Mr. Stelios Louloudakis | slouloudak@ics.forth.gr | +30 2810391293